014-000766

**◆Data**General

**Technical Reference**

Model 10 and 10/SP Computer Systems

#### **Notice**

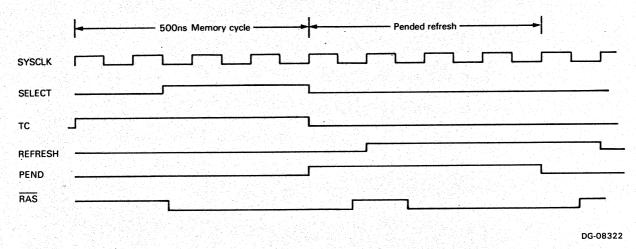

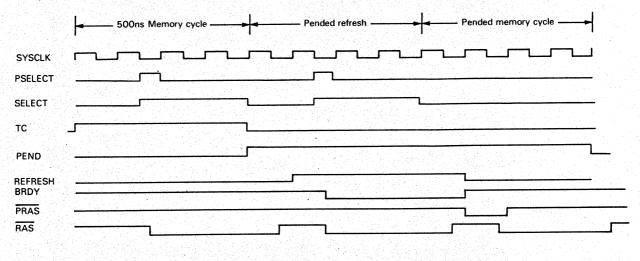

Data General Corporation (DGC) has prepared this document for use by DGC personnel, customers, and prospective customers. The information contained herein shall not be reproduced in whole or in part without DGC's prior written approval.

DGC reserves the right to make changes in specifications and other information contained in this document without prior notice, and the reader should in all cases consult DGC to determine whether any such changes have been made.

The terms and conditions governing the sale of DGC hardware products and the licensing of DGC software consist solely of those set forth in the written contracts between DGC and its customers. No representation or other affirmation of fact contained in this document including but not limited to statements regarding capacity, response-time performance, suitability for use or performance of products described herein shall be deemed to be a warranty by DGC for any purpose, or give rise to any liability of DGC whatsoever.

In no event shall DGC be liable for any incidental, indirect, special or consequential damages whatsoever (including but not limited to lost profits) arising out of or related to this document or the information contained in it, even if DGC has been advised, knew or should have known of the possibility of such damages.

CEO, DASHER, DATAPREP, ECLIPSE, ENTERPRISE, INFOS, microNOVA, NOVA, PROXI, SUPERNOVA, ECLIPSE MV/4000, ECLIPSE MV/8000, TRENDVIEW, MANAP, SWAT, GENAP, and PRESENT are U.S. registered trademarks of Data General Corporation, and AZ-TEXT, DG/L, DG/XAP, GW/4000, ECLIPSE MV/10000, GDC/1000, REV-UP, UNX/VS, XODIAC, DEFINE, SLATE, DESKTOP GENERATION, microECLIPSE, BusiPEN, BusiGEN, and BusiTEXT are U.S. trademarks of Data General Corporation.

Ordering No. 014-000766

© Data General Corporation, 1983 All Rights Reserved Printed in the United States of America Rev. 00, October 1983

# **Preface**

The technical reference manuals for Desktop Generation™ computers and their peripherals are written for assembly language programmers, systems analysts, and engineers. This set of manuals, together with two companion programmer's references, contains the information you need to: 1) write assembly language software, including I/O subroutines; 2) knowledgeably expand your system; 3) learn how your system operates at the card level; and 4) design custom interfaces.

This manual explains the functional and physical organization of Desktop Generation Model 10 and 10/SP computers. Other technical and programmer's references for the Desktop Generation are listed and summarily described under "Related Manuals" in this preface.

## Organization

The manual has three parts: a programming section, a theory of operation section, and a mechanical assemblies section. It also has several appendixes and an index. The chapters in part 1, meant to be read selectively, present the instruction sets for system devices.

- Chapter 1 summarizes the microECLIPSE and 8086 CPU instruction sets and describes in detail those instructions that are unique to the Desktop Generation Model 10 and Model 10/SP CPU. It presents the instructions used to transfer program control between the microECLIPSE processor and the attached 8086 processor.

- Chapter 2 defines the instruction sets and tells you how to program the keyboard and monitor; printer port, real-time clock, programmable interval timer, and diskette controller.

- Chapter 3 describes how to use the firmware console program to do bootstrap loading, assist in debugging programs, and perform system resets.

The chapters in part 2 are also meant to be read selectively. They describe the makeup and operation of the component parts of a standard Desktop Generation Model 10 and Model 10/SP computer system.

- Chapter 4 describes the two-card Desktop Generation Model 10 and Model 10/SP SPU, including the microECLIPSE and 8086 processors, the main memory and MAP unit, the keyboard and monitor interfaces, the diskette interface, the printer port, real-time clock, and programmable interval timer. The chapter also discusses the floating-point option, the power-up self test, and the on-card virtual console.

- Chapter 5 describes the theory of operation of the optional dynamic randomaccess memory card.

- Chapter 6 discusses the operation of an optional color video interface card.

- Chapter 7 provides a description of the Desktop Generation power supply.

The chapter in part 3 illustrates the mechanical components of the Model 10 and 10/SP computer system.

- Chapter 8 contains a description of the physical modules and their configurations as well as the system cabling scheme.

- Appendix A lists the numbers of available logic schematics and wiring lists.

- Appendix B summarizes the diagnostic assembly language instructions for the diskette.

- Appendix C presents a listing of some typical assembly language code used to manage the 8086 processor from a microECLIPSE program.

- Appendix D explains the format in which words must be written into the monochrome monitor screen buffer in order for the data to be displayed on the screen.

- The index alphabetically lists the concepts and terms in this book and references the pages on which they appear.

A documentation comment form follows the index. It invites you to help Data General improve its publications by commenting on this book.

vorhanden

#### **Related Manuals**

A comprehensive documentation set supports all the hardware and software products available for Desktop Generation computers. The hardware-related books listed below fall into three categories: the technical reference series; the user guides for operating, installing, and testing; and the introductory guide for Desktop Generation computers.

The following technical and programmer's references address the needs of assembly language programmers and engineers.

#### 16-bit Real Time ECLIPSE Assembly Language Programming

Global in nature, this book explains the processor-independent concepts, functions, and instruction sets of 16-bit ECLIPSE computers. DGC ordering no. 014-000688.

# Model 10 and 10/SP System Console Programmer's Reference

Describes the organization and alphanumeric and graphic features of the system console. Defines the command sets and includes guidelines for programming the monochrome and optional color monitors at assembly and high-level language levels. DGC ordering no. 014-000770.

#### Model 20 and 30 Computer Systems Technical Reference

In addition to the functional and physical organization of Model 20 and 30 computers and their technical specifications, this manual explains their processor-unique concepts, functions, and instruction set features. Also included are guidelines for programming the I/O devices, including the diskette subsystem, and a theory of operation for the basic components of Models 20 and 30. DGC ordering no. 014-000767.

#### I/O and Interfacing Technical Reference

Introduces the microI/O bus and describes the I/O interface required to communicate with this bus and its host Desktop Generation computer. Discusses the I/O instruction set and the I/O program interrupt and data channel facilities. Includes a chapter about the 4210 general-purpose interface, useful to those designing a custom I/O interface for their system. DGC ordering no. 014-000774.

For more detailed information about the microI/O bus and Data General integrated circuits used in the I/O interface, refer to *microNOVA Integrated Circuits Data Manual*. DGC ordering no. 014-000074.

# Model 6271 Disk Subsystem Technical Reference

Describes the functional and physical organization of the Model 6271 disk subsystem. Defines the I/O instruction set and provides guidelines for programming the subsystem. DGC ordering no. 014-000768.

# Communications Interfaces Technical Reference

Discusses the functional and physical organization of the asynchronous/ synchronous communications interfaces available for Desktop Generation computers. Defines their I/O instruction sets, offers guidelines for writing assembly language I/O subroutines, and contains theory of operation for each communications card. DGC ordering no. 014-000769.

# Sensor I/O Technical Reference

Defines instruction sets, offers guidelines for writing assembly language I/O subroutines, describes theory of operation at an overview level, and explains how to connect field wiring for the 4222 digital I/O interface, 4223 analog-to-digital interface, 4224 digital-to-analog interface, and 4335 analog subsystem. DGC ordering no. 014-000775.

#### IEEE-488 Bus Interface Technical Reference

Provides the information needed to interface, program in assembly language, and troubleshoot this card in a Desktop Generation system. Reviews the contents of the IEEE-488 bus standard, summarizing its commands, messages, and states, and includes a theory of operation. DGC ordering no. 014-000773.

The following books are how-to manuals written for anyone who needs to know how to install; operate, and test a Desktop Generation system.

#### Installing Model 10 and 10/SP Systems

The first book that a Model 10 or 10/SP owner should read, explains how to unpack and install either system and its optional peripherals. Simple instructions and ample illustrations make the book accessible to any reader. DGC ordering no. 014-000901.

#### Operating Model 10 and 10/SP Systems

A logical follow-on to Model 10 and 10/SP installation, this guide takes you from powering up the system and its optional peripherals through performing such routine operations as loading paper in a printer and inserting or removing diskettes. Brings you to the point of loading the system software. Amply illustrated and written for users at any level of experience. DGC ordering no. 014-000900.

#### Testing Model 10 and 10/SP Systems

Follows the installation and operating manuals with instructions for verifying the operation of Model 10 or 10/SP systems and their optional peripherals. Steps you through the power-up test and Customer Diagnostics and explains how to troubleshoot customer-replaceable components. Simple instructions and diagrams make the book accessible to any user. Includes phone numbers for Data General assistance. DGC ordering no. 014-000902.

#### **Installing Model 20 and 30 Systems**

The first book a Model 20 or 30 owner should read, explains how to unpack and install either system and its optional peripherals. Accessibly written and illustrated, for users at any level of experience. DGC ordering no. 014-000904.

#### Operating Model 20 and 30 Systems

Follows Model 20 and 30 installation, leading you from powering up the system and its optional peripherals through performing such routine operations as loading paper in a printer and inserting or removing diskettes. Brings you to the point of loading the system software. The simple instructions and generous illustrations are suitable for any reader. DGC ordering no. 014-000903.

#### Testing Model 20 and 30 Systems

A follow-on to the installation and operating manuals, explains how to verify the operation of Model 20 or 30 systems and their optional peripherals. Simple instructions and diagrams lead you through the power-up test, Customer Diagnostics, and trouble-shooting of customer-replaceable components. Includes phone numbers for Data General assistance. DGC ordering no. 014-000905.

This last book is a product overview, addressed to all Desktop Generation users.

#### The Desktop Generation

Introduces the Desktop Generation, summarizing each model of the family, and describes its many hardware and software products, features, and capabilities. Includes a brief history of Data General, a sampling of applications, and an overview of the customer service and support programs available to you as a Desktop Generation user. DGC ordering no. 014-000751.

#### Conventions

The following conventions are used throughout this manual.

MNEMONIC Uppercase sans serif letters indicate a signal name or instruc-

tion mnemonic. When a signal is active low, it is barred—for

example, FDCHE.

argument Italicized lowercase letters mean that a particular instruction

takes an argument. In your program, you must replace this

symbol with the exact code for the argument you need.

[optional] Brackets signify an optional argument. If you decide to use this

argument, do not include the brackets in your code; they only

set off the choice.

In dialogs between system and user, we use this typeface to show your input:

#### **USER INPUT**

and this typeface to show the system's response:

#### SYSTEM RESPONSE.

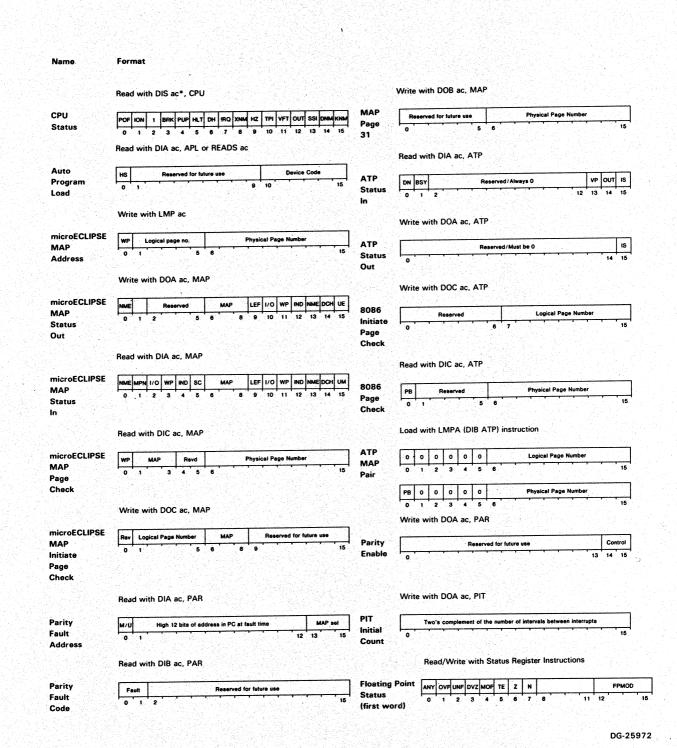

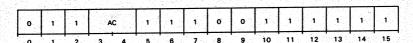

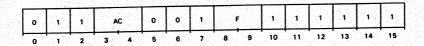

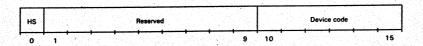

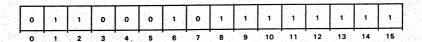

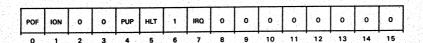

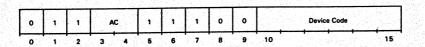

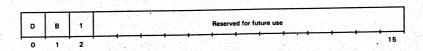

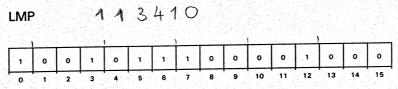

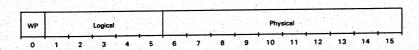

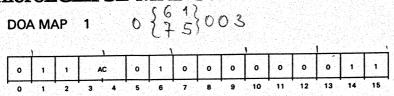

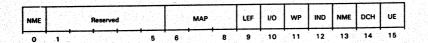

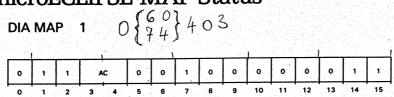

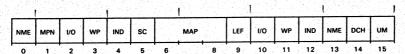

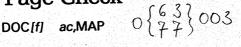

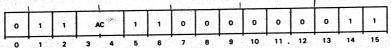

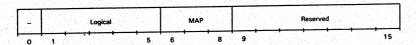

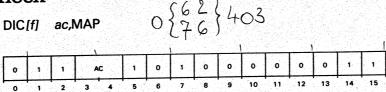

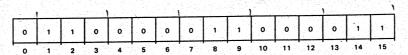

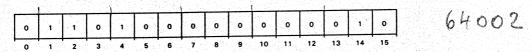

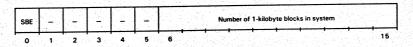

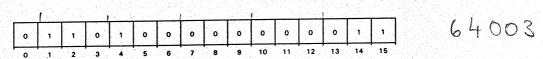

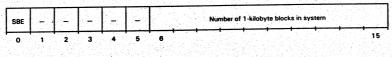

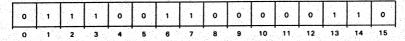

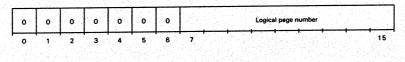

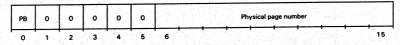

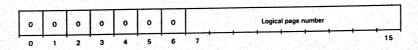

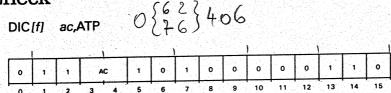

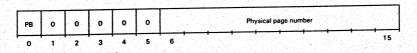

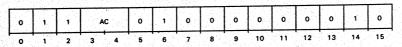

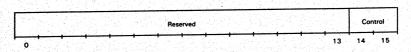

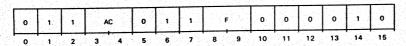

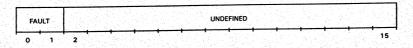

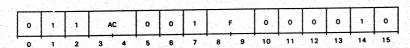

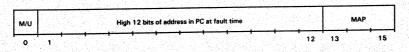

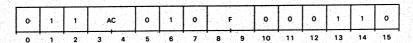

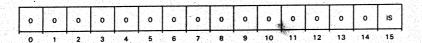

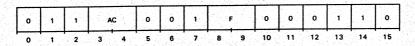

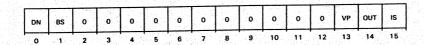

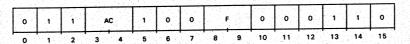

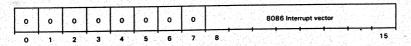

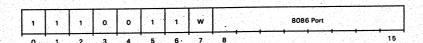

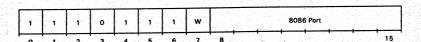

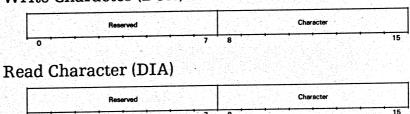

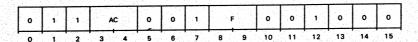

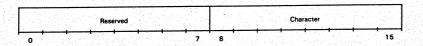

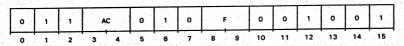

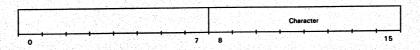

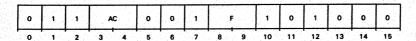

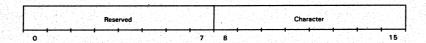

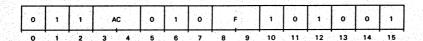

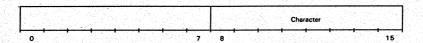

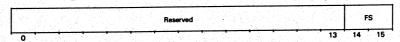

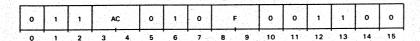

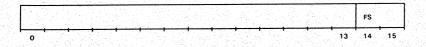

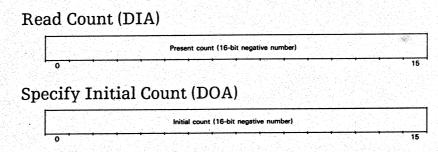

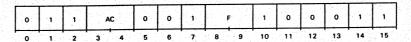

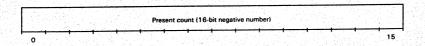

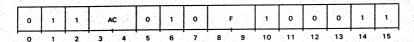

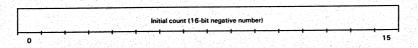

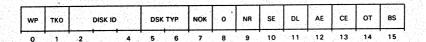

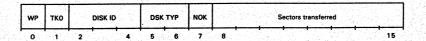

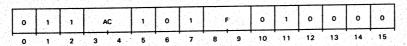

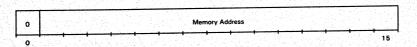

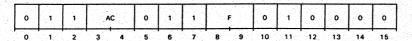

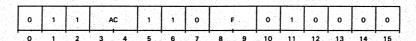

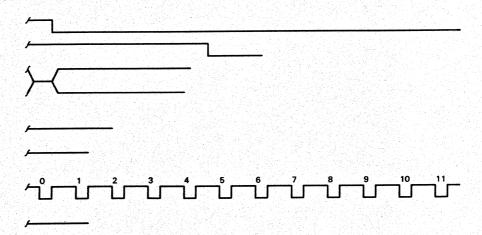

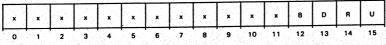

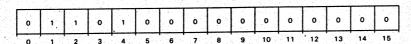

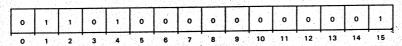

In addition, we use the following diagram to show the arrangement of the 16 bits in an instruction. The diagram is always divided into 16 boxes, numbered 0 through 15.

# Contents

|      | Preface                                                      |          |

|------|--------------------------------------------------------------|----------|

|      | Organization                                                 | ii       |

|      | Related Reading                                              | 111      |

|      | Conventions                                                  | <b>v</b> |

|      | System Overview                                              |          |

|      | Configurations                                               | 2        |

|      | Organization                                                 | J        |

|      | Components                                                   | ວ        |

|      | System Processing Unit                                       | o        |

|      | Diskette Subsystem                                           | 0        |

|      | Disk Subsystem                                               | 9        |

|      | Video Interface                                              | 9        |

|      | System Console                                               | 9        |

|      | Multiterminal Workstations                                   | 9        |

|      | Cartridge Tane Subsystem                                     | 9        |

|      | I/O Interfaces                                               | 9        |

|      | Power Subsystem                                              | 10       |

|      | Technical Specifications                                     | 10       |

| ONE  | Programming                                                  |          |

| OIVE | [편집] : 사이트 1호 교사에서 불발 보다 가장 사람들이 바람들이 되었습니다. 그리는 사람들이 되었습니다. |          |

| 1    | Programming the CPUs                                         |          |

|      | Model 10 and 10/SP Dual-Processor System                     | 1-2      |

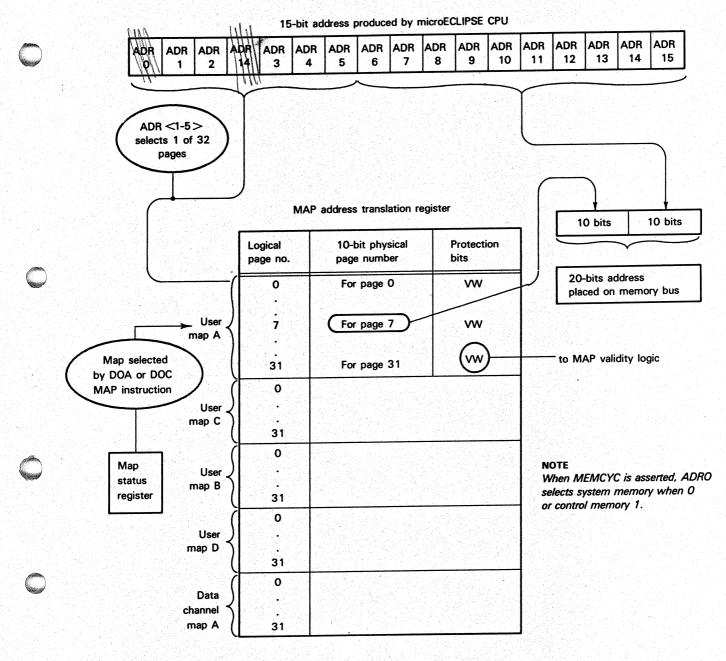

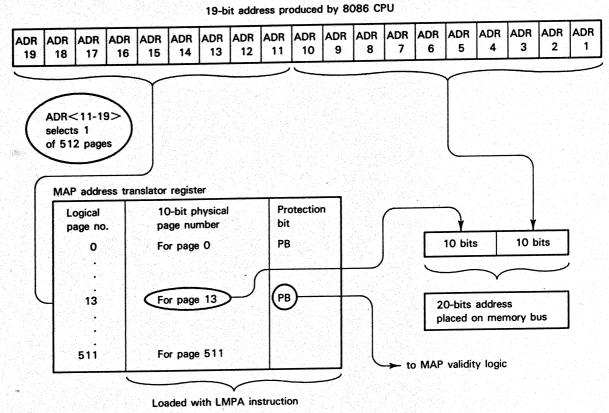

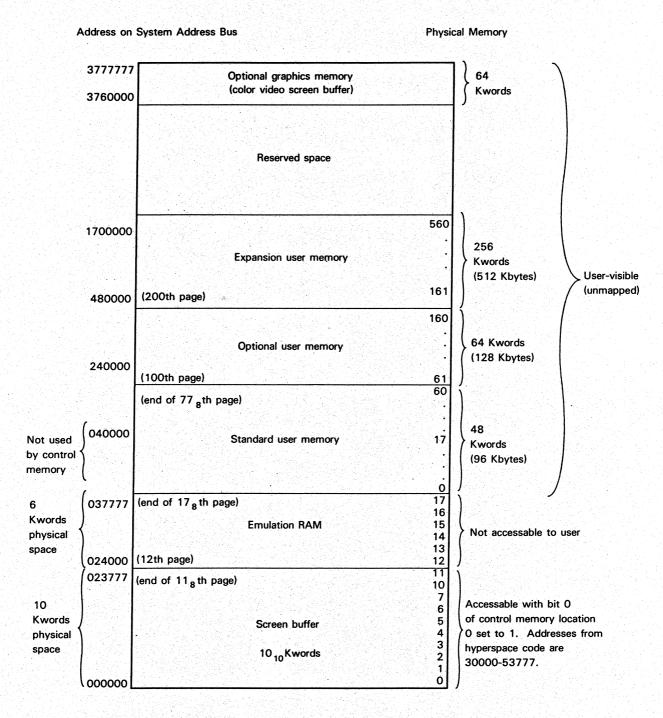

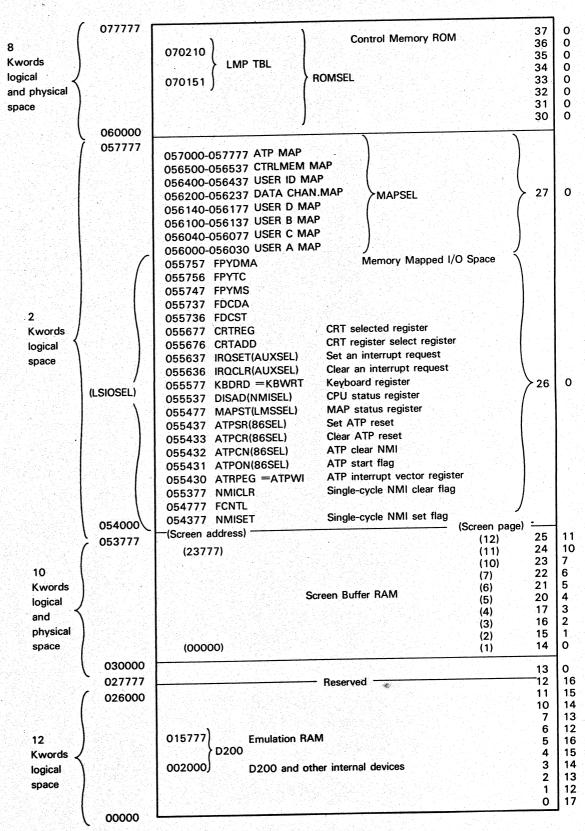

|      | System Memory Mapping                                        | 1-3      |

|      | Parity Checking                                              | . 1-     |

|      | MicroECLIPSE CPU Features                                    | 1-3      |

|      | Addressing                                                   | 1-4      |

|      |                                                              |          |

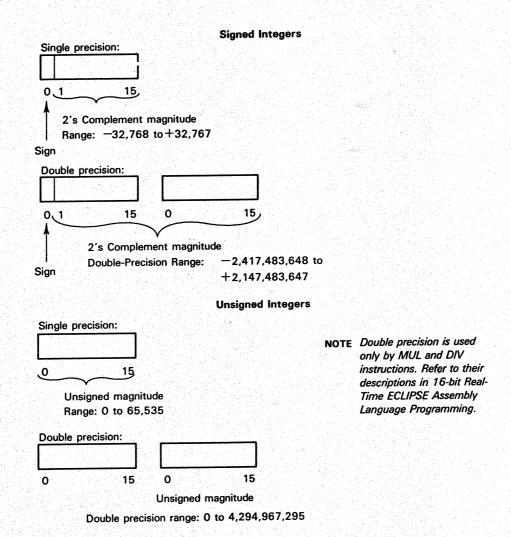

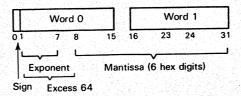

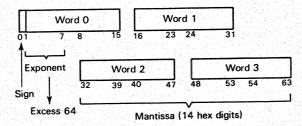

|   | Data Formats                                                 |        |

|---|--------------------------------------------------------------|--------|

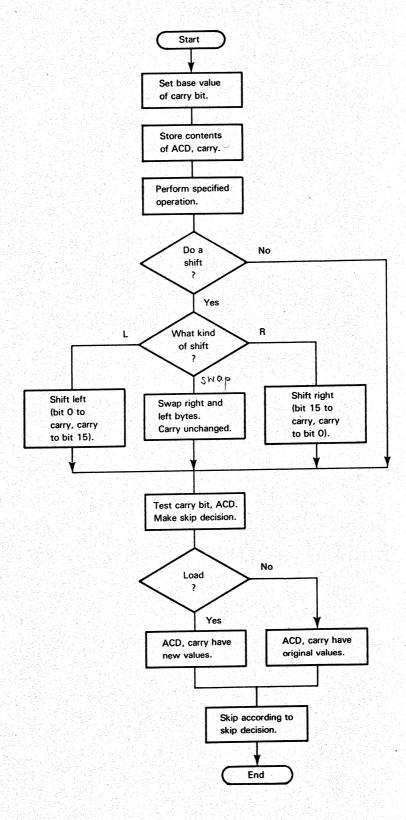

|   | Arithmetic/Logic Class Operations                            | 1-8    |

|   | Stack Operations                                             | . 1-10 |

|   | Floating-Point Operations                                    | . 1-10 |

|   | String Operations                                            | . 1-10 |

|   | MAP Operations                                               | 1-11   |

|   | Extended Operations                                          | . 1-12 |

|   | Emulator Trap                                                | .1-12  |

|   | Parity Check Operations                                      | . 1-12 |

|   | I/O Operations                                               | 1-12   |

|   | Program-Accessible Registers                                 | . 1-13 |

|   | MicroECLIPSE Instructions                                    | . 1-16 |

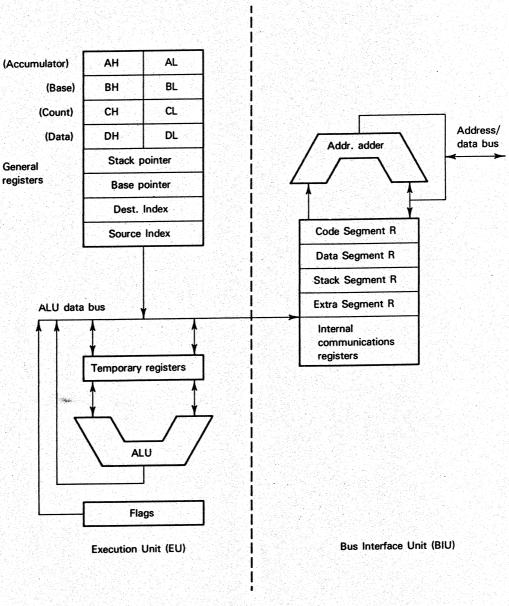

|   | 8086 CPU Features                                            | . 1-28 |

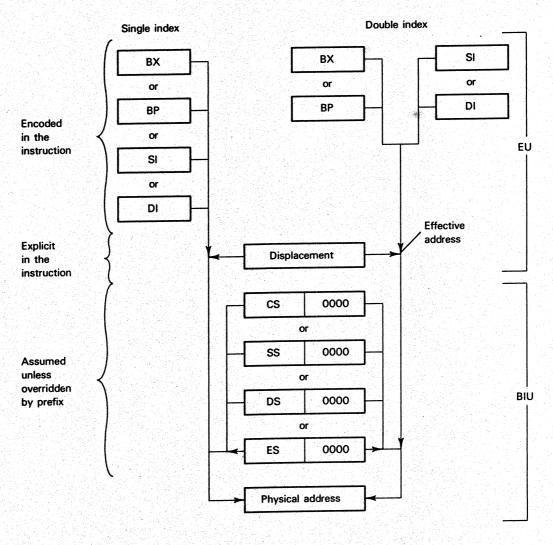

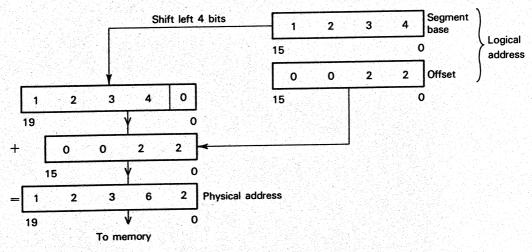

|   | 8086 Memory Segmentation                                     | 1-29   |

|   | 8086 Addressing Modes                                        | 1-29   |

|   | Segment Registers                                            | . 1-31 |

|   | Input/Output                                                 | 1-33   |

|   | Instructions                                                 | . 1-33 |

|   | Processor Programming                                        | . 1-37 |

|   | SPU Power-Up Response                                        | . 1-37 |

|   | microECLIPSE CPU Status Register                             | 1-40   |

|   | Program Load Register                                        | .1-41  |

|   | Memory Allocation and Protection                             | 1-43   |

|   | Programming the MAPs                                         | 1-59   |

|   | Parity Checking                                              | 1-61   |

|   | The 8086 Attached Processor                                  |        |

|   | Programming Bit-Mapped Graphics                              | . 1-70 |

|   | Powerfail/Autorestart                                        | . 1-71 |

|   | Instruction Execution Times                                  |        |

|   | 발표는 보통하고 모르다 있다. 그리고 하는 사람들은 사람들은 그렇지만 모르는 생활이 하를 받았다면 살아왔다. |        |

| 2 | Programming CPU-Resident I/O Devices                         |        |

|   | System Console Interface                                     | 2-1    |

|   | Programmable Elements                                        |        |

|   | Programming Summary                                          | 2-2    |

|   | Registers and Flags                                          | 2-4    |

|   | I/O Instruction Set                                          |        |

|   | Programming Guidelines                                       | 2-7    |

|   | Reading Characters                                           |        |

|   | I/O Timing                                                   |        |

|   | Power-Up Response                                            |        |

|   | Printer Port                                                 |        |

|   | Programmable Elements                                        | 2-9    |

|   | Programming Summary                                          | 2-9    |

|   | Registers and Flags                                          | . 2-12 |

|   | I/O Instruction Set                                          | . 2-13 |

|   | 그렇게 되는 방에 어려움을 하다는 하다 시간 이 이름 눈에 있는 그의 교육을 됐다면 되었습니다. 한 경험들이 되고 있다. 사용이 이용의 이용의 제가를 하는 것으로 되었습니다. 그 모모 | 0.15   |

|---|--------------------------------------------------------------------------------------------------------|--------|

|   | Programming Guidelines                                                                                 | 2-15   |

|   | Reading Characters                                                                                     | . 2-15 |

|   | I/O Timing                                                                                             | .Z-10  |

|   | Power-Up Response                                                                                      | . 2-18 |

|   | Real-Time Clock Interface                                                                              | . 2-18 |

|   | Programmable Elements                                                                                  | 2-18   |

|   | Programming Summary                                                                                    | . Z-18 |

|   | Registers and Flags                                                                                    | .2-19  |

|   | I/O Instruction Set                                                                                    | . 2-20 |

|   | Programming Guidelines                                                                                 | . Z-Z1 |

|   | I/O Timing                                                                                             | . 2-22 |

|   | Device In Passance                                                                                     | . 2-22 |

|   | Programmable Interval Timer                                                                            | . 2-22 |

|   | Programmable Elements                                                                                  | . 2 22 |

|   | Programming Summary                                                                                    | . 2-22 |

|   | Registers and Flags                                                                                    | 2-24   |

|   | T/O Instruction Set                                                                                    | . 2-25 |

|   | Programming Guidelines                                                                                 | 2-21   |

|   | I/O Timing                                                                                             | 2-21   |

|   | Power-Up Response                                                                                      | 2-21   |

|   | Diskette Subsystem                                                                                     | 2-28   |

|   | Programmable Elements                                                                                  | 2-28   |

|   | D                                                                                                      | 2-28   |

|   | Registers and Flags                                                                                    | Z-31   |

|   | T/O Instruction Set                                                                                    | 2-32   |

|   | Programming Guidelines                                                                                 | 2-41   |

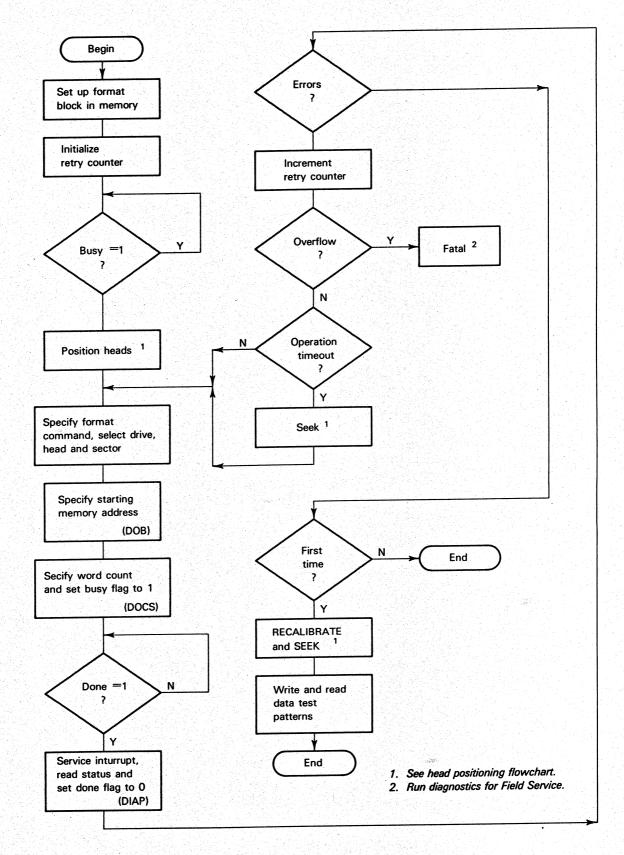

|   | Reformatting a Diskette                                                                                | Z-4/   |

|   | I/O Timing                                                                                             | 2-56   |

|   | Error Conditions                                                                                       | 2-30   |

|   | Power-Up Response and Initial Program Load                                                             | 2-09   |

| 3 | Virtual Console                                                                                        |        |

|   | Cells                                                                                                  | 3-3    |

|   | Formats                                                                                                | 3-3    |

|   | Cell Commands                                                                                          | 3-4    |

|   | Function Commands                                                                                      | 3-5    |

|   | Breakpoints and Program Control                                                                        | 3-5    |

|   | Additional Commands                                                                                    | 3-8    |

|   | Correcting Errors                                                                                      | 3-8    |

|   | The Rubout Key                                                                                         | 3-8    |

|     | The K Command Virtual Console Errors          |       |

|-----|-----------------------------------------------|-------|

| TWO | Theory of Operation                           |       |

| 4   | System Processing Unit                        |       |

|     | Architecture: Major Elements                  | 4-4   |

|     | CPU Section                                   |       |

|     | Control Memory                                | 4-9   |

|     | Bus Arbitration and DMA and I/O Control Logic | 4-10  |

|     | Multidevice/microI/O Bus Section              | 4-10  |

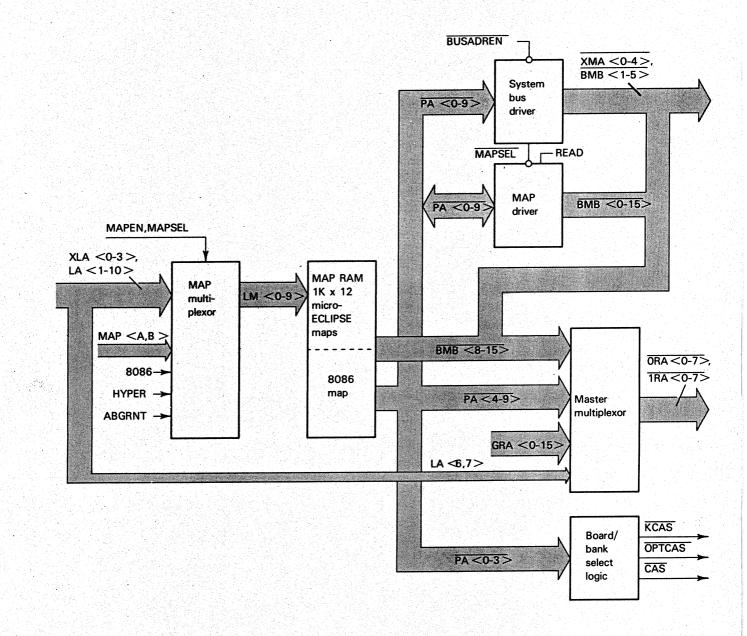

|     | MAPs and Master Multiplexor                   |       |

|     | Oncard Memory and Parity Logic                |       |

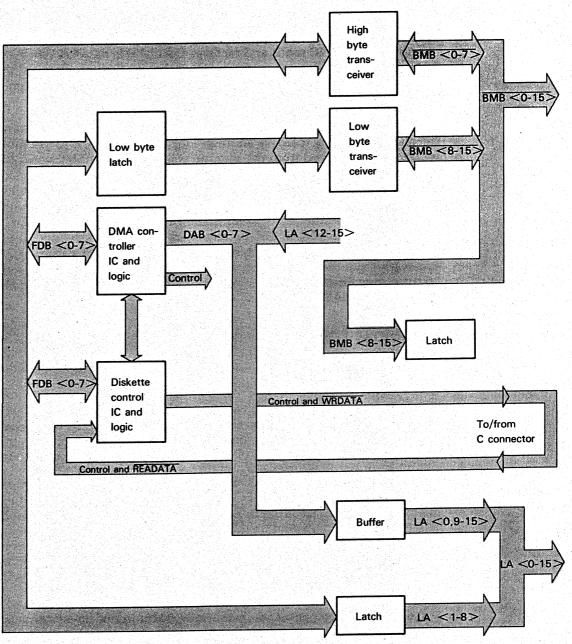

|     | Diskette Interface                            |       |

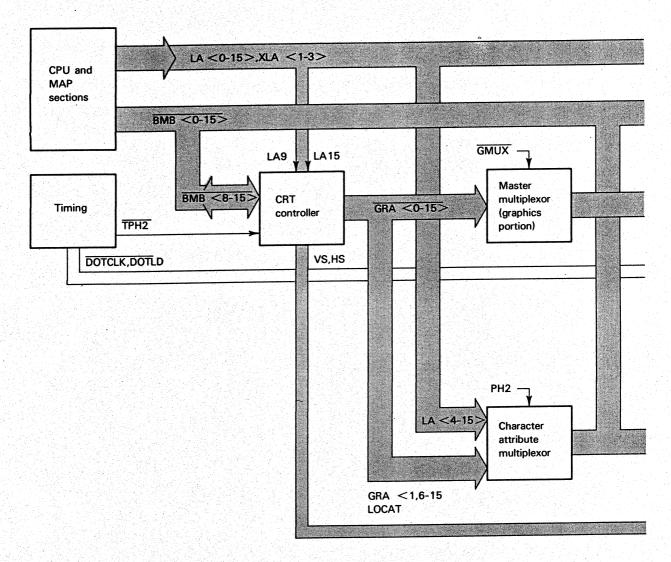

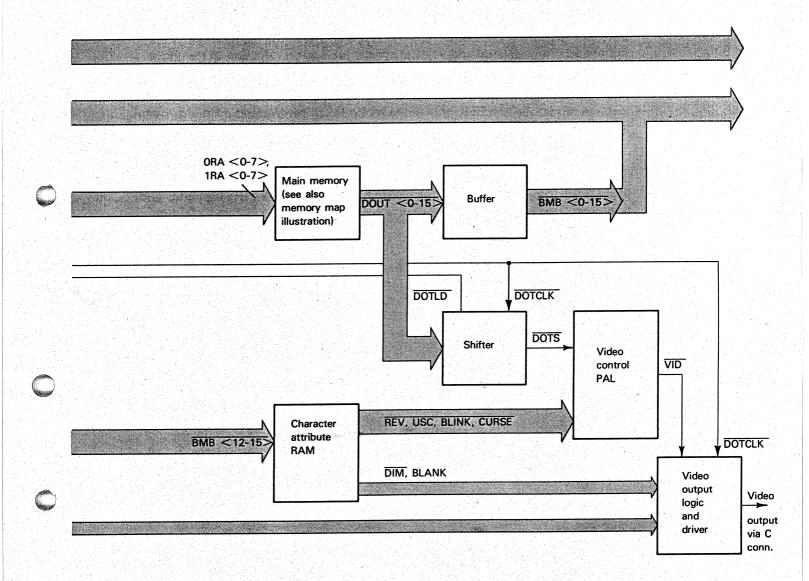

|     | System Console Interface                      |       |

|     | Decode and Timing Logic                       |       |

|     | Operational Overview                          |       |

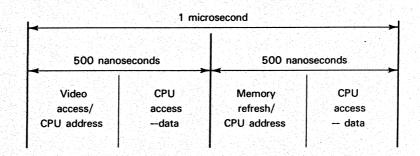

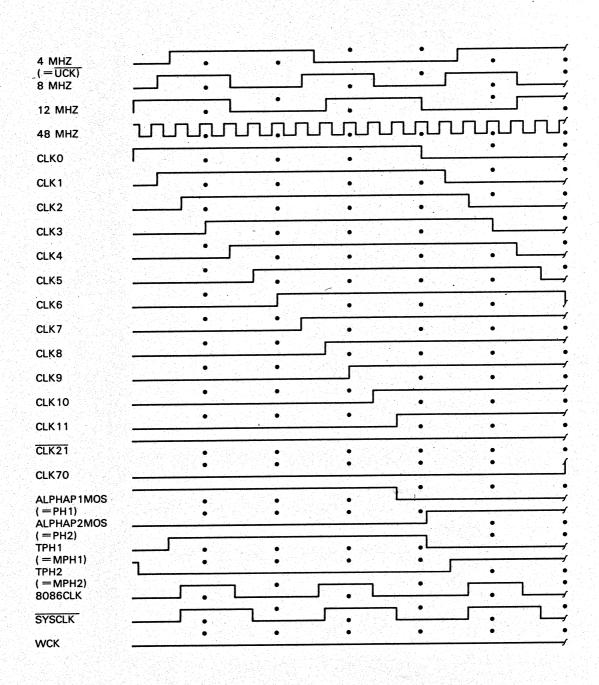

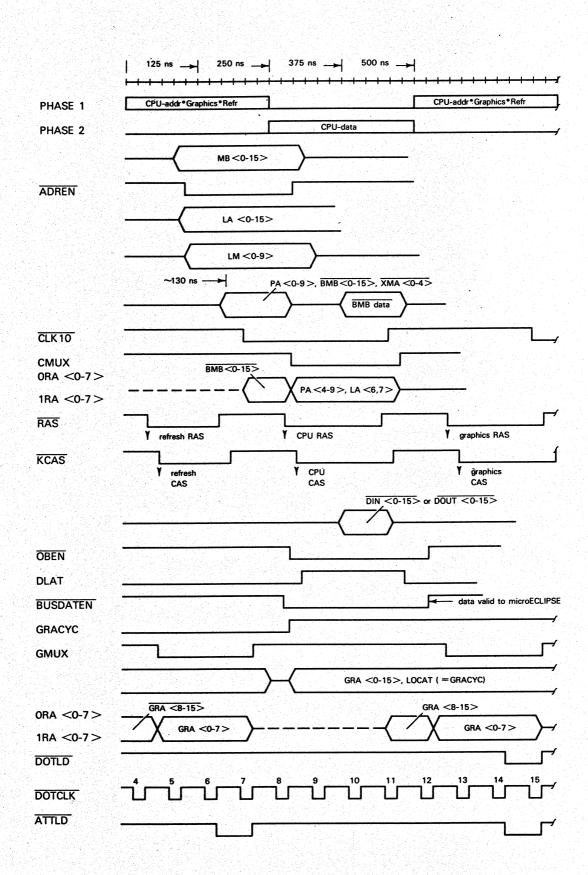

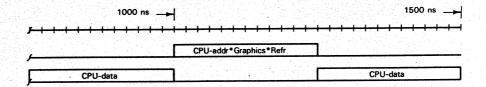

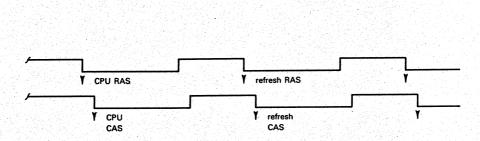

|     | System Timing                                 | 4-33  |

|     | Signals                                       | 4-38  |

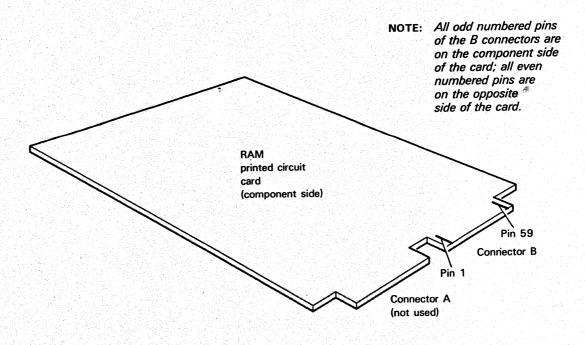

| 5   | Optional Memory Card                          |       |

|     | Installation and Jumpering                    | , 5-2 |

|     | Interfacing                                   | 5-2   |

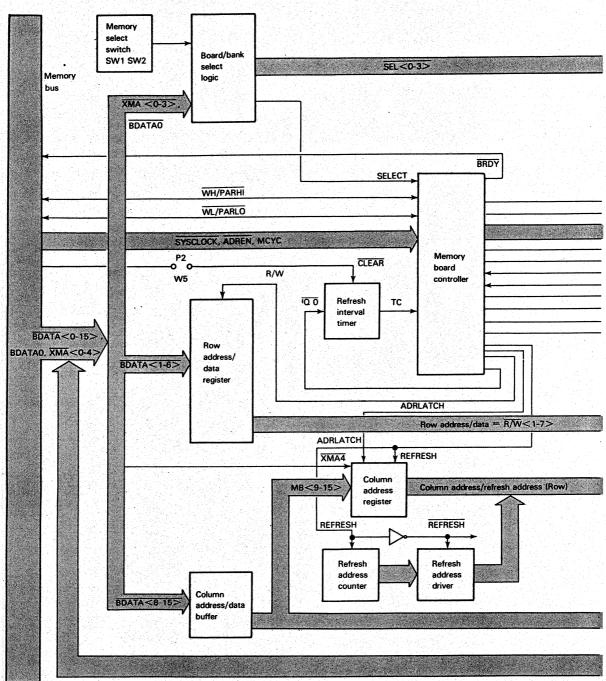

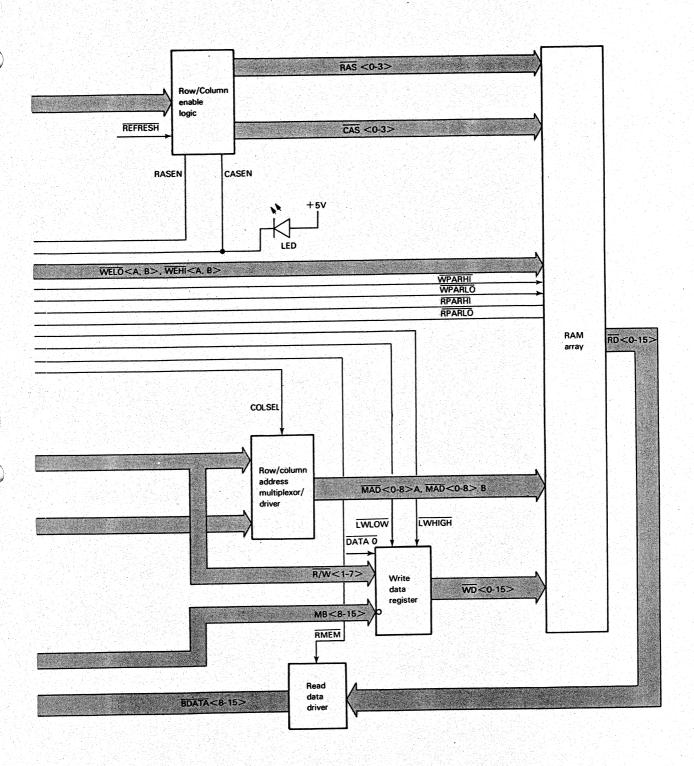

|     | Theory of Operation                           | 5-4   |

|     | Initiating a Memory Operation                 |       |

|     | Row and Column Address Selection              |       |

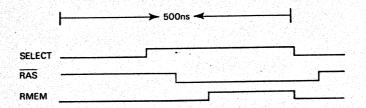

|     | Read                                          |       |

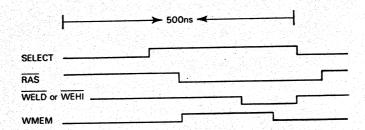

|     | Write                                         |       |

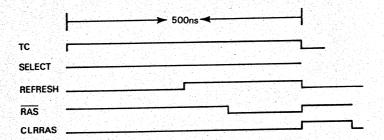

|     | Refresh                                       | 5-8   |

| 6   | Optional Video Interface                      |       |

|     | To Be Supplied                                | 6-1   |

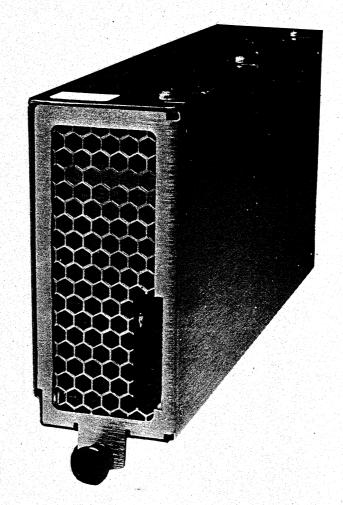

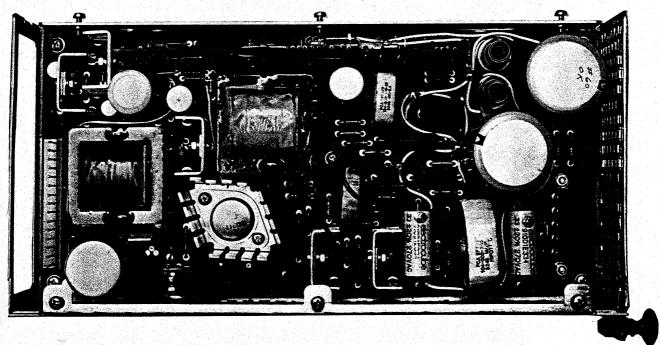

| 7   | Power Supply Assembly                         |       |

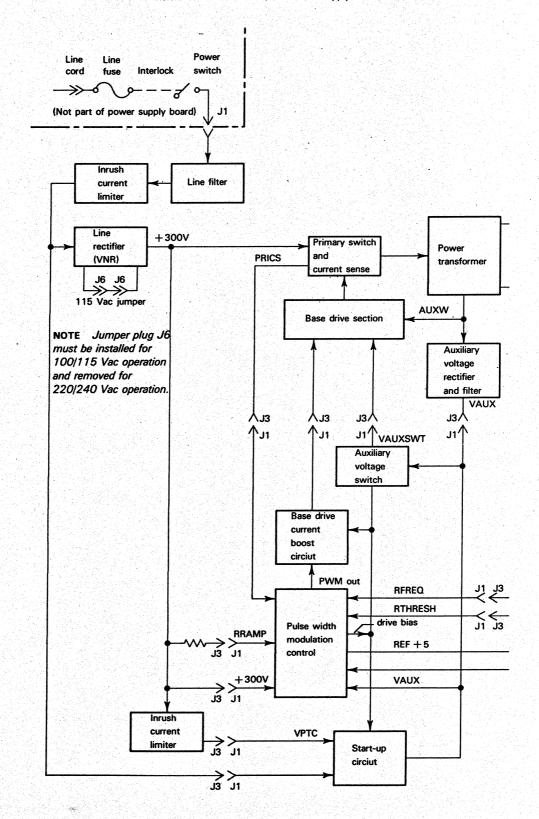

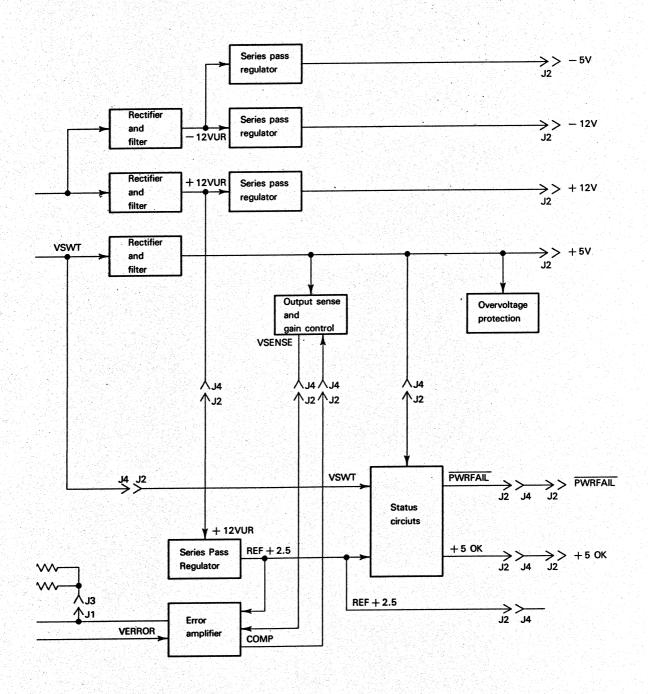

|     | Theory of Operation                           | 7-2   |

|     | Line Rectification                            |       |

|     | Start-up Circuit                              | 7-6   |

|     | Power Section                                 | 7-6   |

|     | Output Section                                | 7-8   |

|     | Auxiliary Voltage Section                     |       |

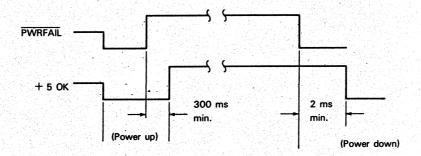

|     | Status Circuits                               | 7-10  |

|     | Interconnection with the System               | 7-10  |

| THREE                                                 | Mechanical Assemblies                               |             |

|-------------------------------------------------------|-----------------------------------------------------|-------------|

| 8                                                     | Model 10 and Model 10/SP Modules and Configurations |             |

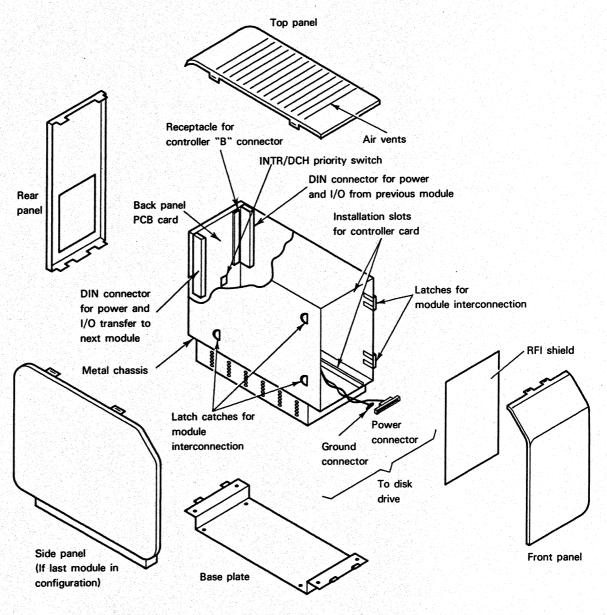

|                                                       | Unit Architecture                                   | 8-2         |

|                                                       | Power Supply Module (PM)                            | 8-4         |

|                                                       | CPU Logic Module (CLM)                              | 8-5         |

|                                                       | Logic Expansion Module (LEM)                        | 8-6         |

|                                                       | Disk Modue (DM)                                     | 8-6         |

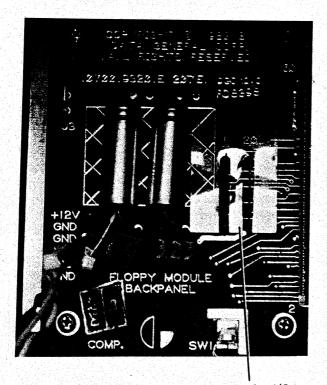

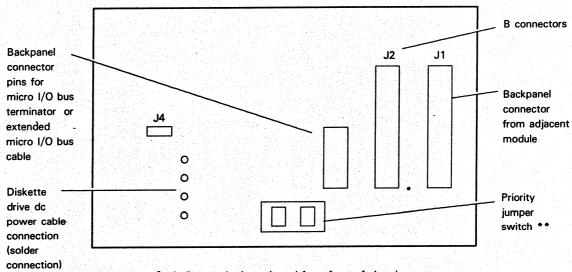

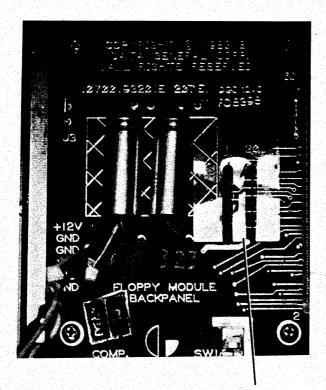

|                                                       | Diskette Module (FM)                                | 8-6         |

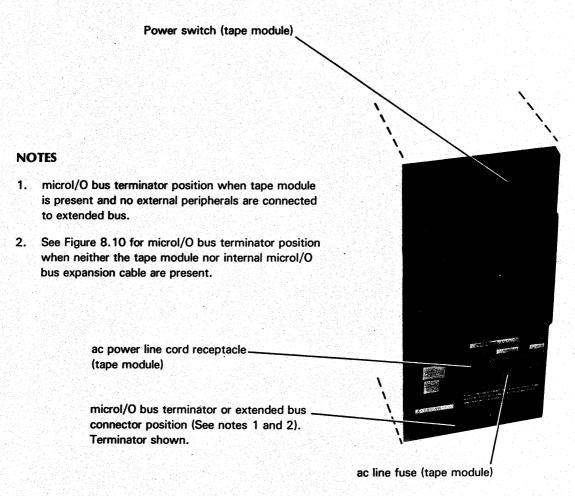

|                                                       | Tape Module (TM)                                    | 8-6         |

|                                                       | Configurations                                      | 8-6         |

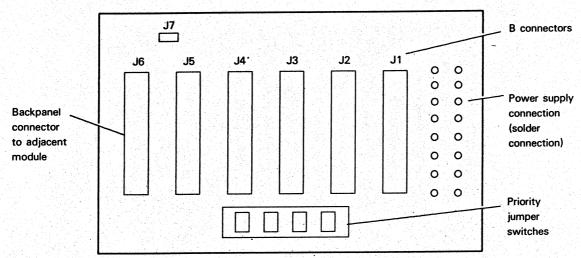

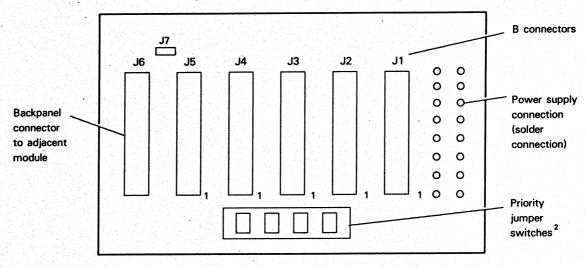

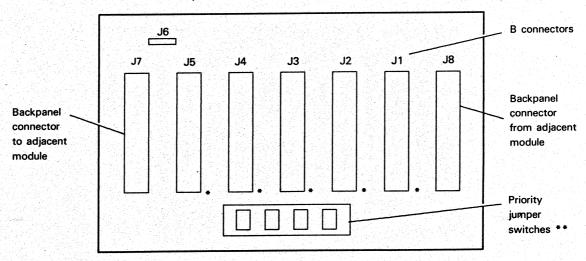

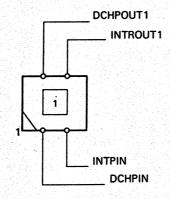

|                                                       | Module Architecture                                 | 8-8         |

| 마음 및 이 부하지 않는다.<br>하는 이 역 등 등 등 등 등 등                 | Power Bus                                           | 8-11        |

|                                                       | Memory Bus                                          | 8-11        |

|                                                       | Input/Output Bus                                    | 8-11        |

|                                                       | Slot Assignments                                    | 8-14        |

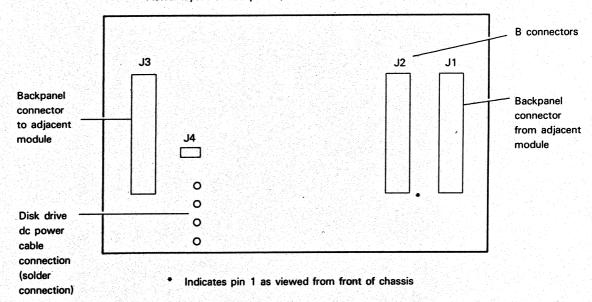

|                                                       | Backpanel Pin Assignments                           | 8-19        |

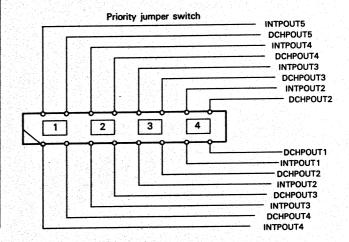

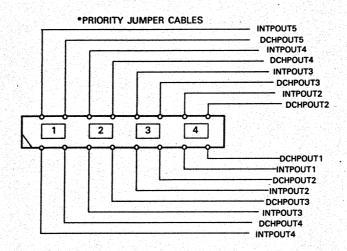

|                                                       | Backpanel Priority Switches                         | 8-26        |

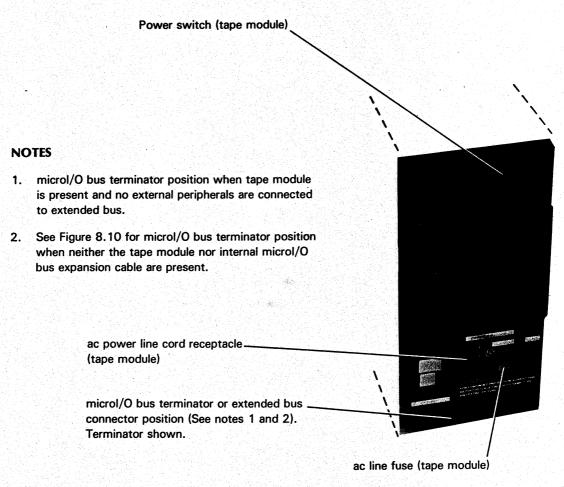

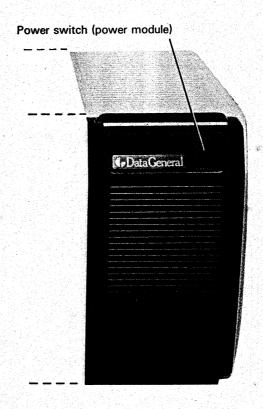

|                                                       | Power Switch                                        | 8-26        |

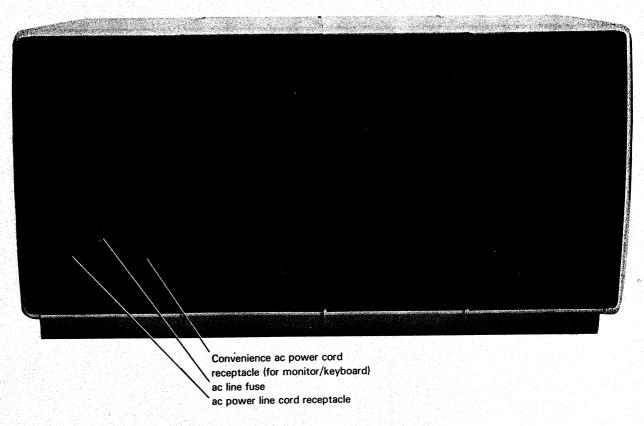

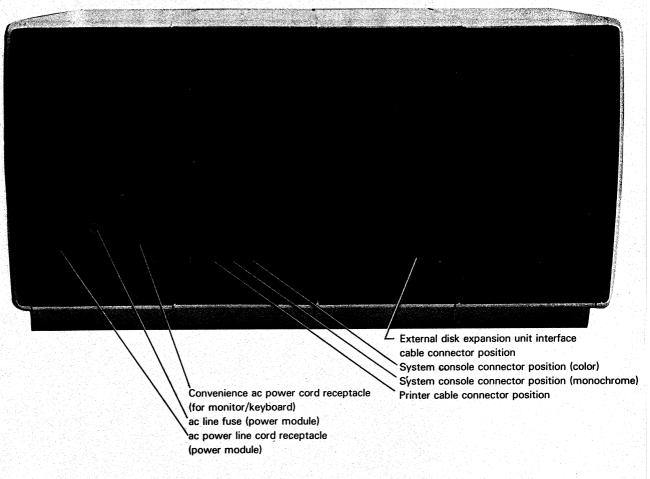

|                                                       | Line Fuses                                          | 8-29        |

|                                                       | Power Interlock                                     | 8-29        |

|                                                       | System Cables                                       | 8-29        |

| Α                                                     | Related Drawings                                    |             |

| В                                                     | Diskette Diagnostic Commands                        |             |

| C                                                     | ATP Interface Programming Example                   |             |

| $\mathbf{D}$                                          | Memory Formats for Bit-Mapped Screen Buff           | er          |

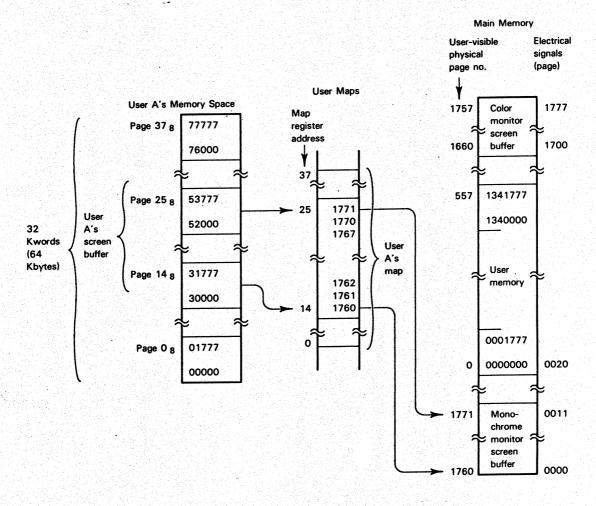

|                                                       | Memory Mapping the Screen Buffer                    | D-1         |

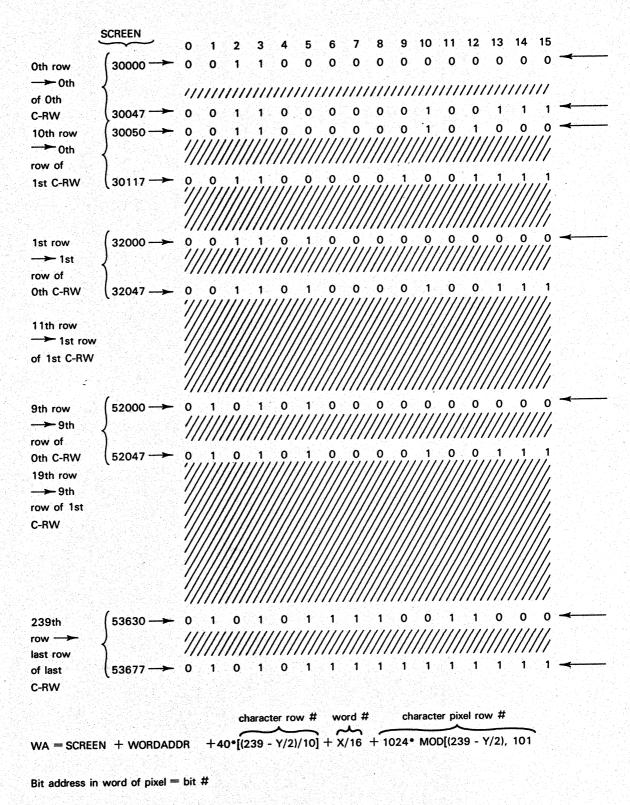

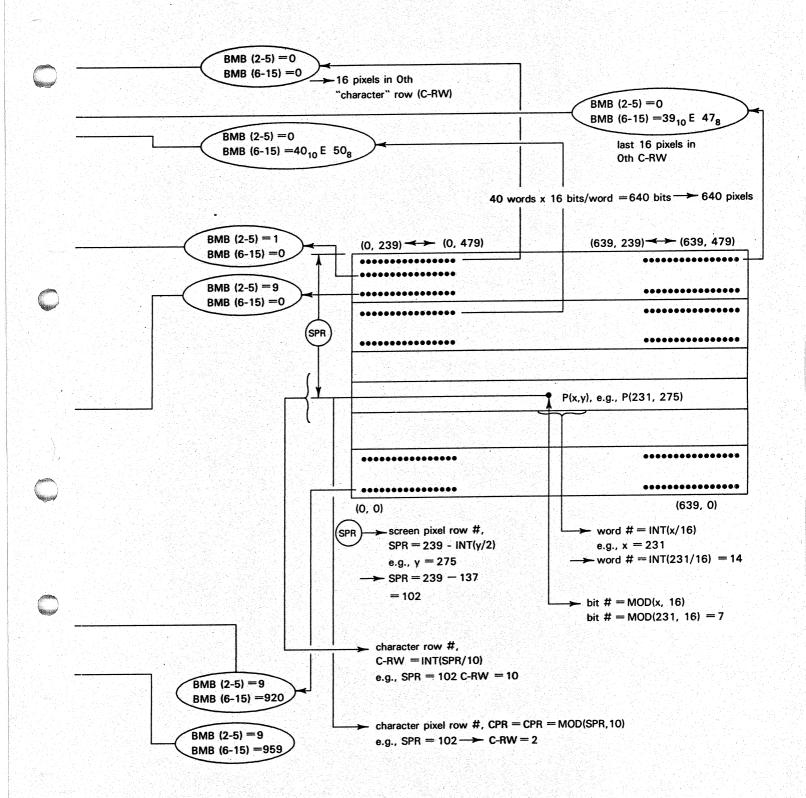

|                                                       | Mapping Screen Pixels to the Buffer                 | <b>D</b> -3 |

| 10.5 2 10 13 13<br>1 13 13 13 13 13 13 13 13 13 13 13 | Character Cell Attributes                           | D-7         |

|                                                       | Attribute Addressing                                | D-7         |

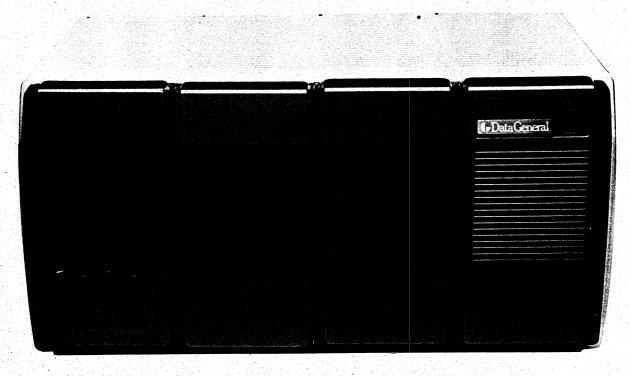

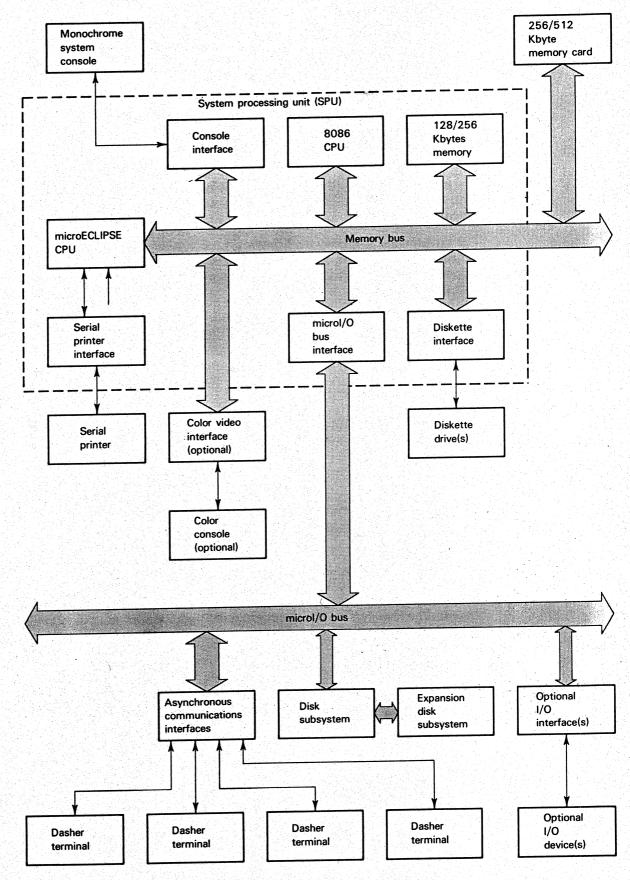

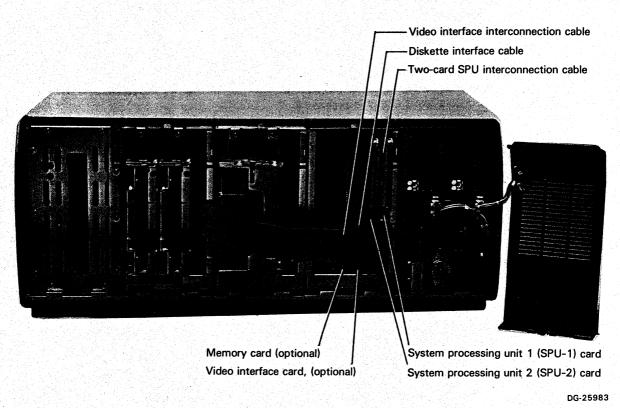

Figure 0-1 Models 10 or 10/SP computer systems

PH-0726

# Overview

Model 10 and Model 10/SP systems are dual-processor desktop computers designed for multi-user commercial and technical applications. Used as technical workstations or applications in business, education, science, real-time control, and industrial automation arenas, they offer minicomputer power in a desktop unit.

This chapter provides an overview of the Model 10 and Model 10/SP Desktop Generation computer systems. It discusses their configurations and functional organization and briefly describes their major components, including: the

system processors, their memories, the diskette and Winchester disk subsystems, the power subsystem, the system console (display monitor and keyboard), and the optional cartridge tape subsystem, communications multiplexors, and input/output (I/O) interfaces. System technical specifications conclude the chapter.

# **Configurations**

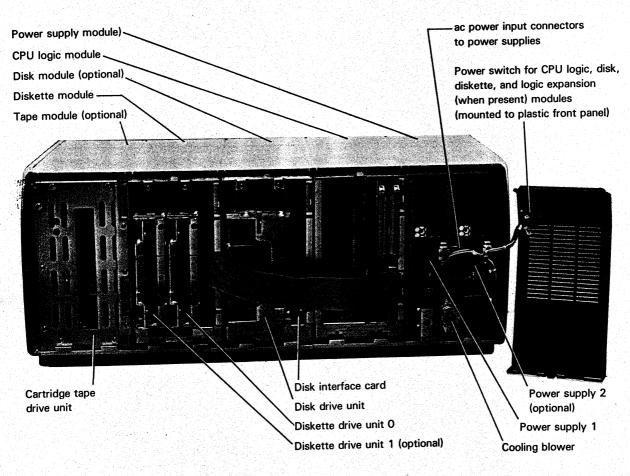

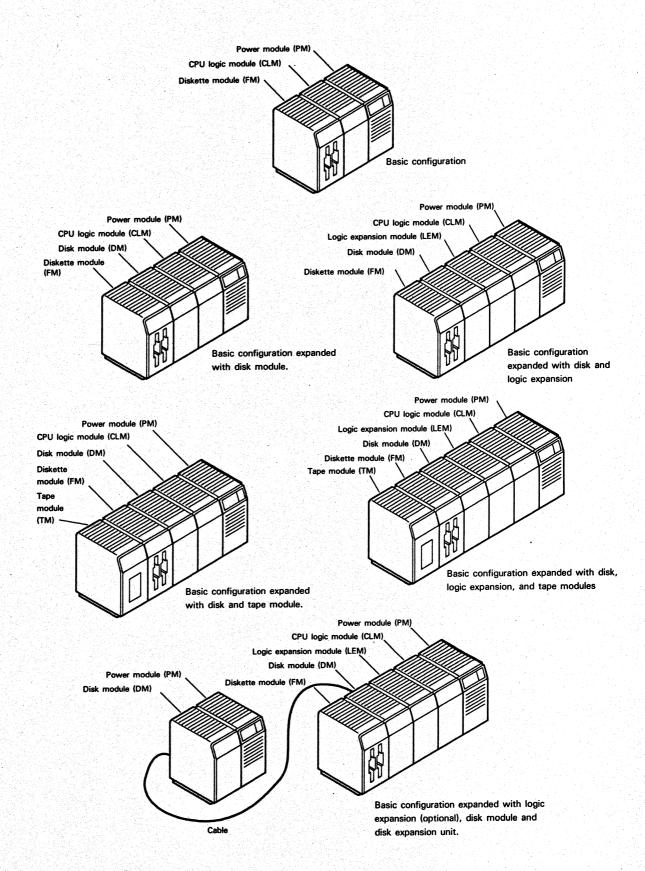

The Model 10 and Model 10/SP systems are identical to each other except that the Model 10/SP is configured with a firmware floating point feature to support AOS and MP/AOS-SU operating systems. The systems use a common set of modular building blocks, identical in size, that interconnect for ease of installation and system expansion. The set consists of the following modules:

power module

5-slot CPU logic module

diskette module

disk module

5-slot logic expansion module

cartridge tape module

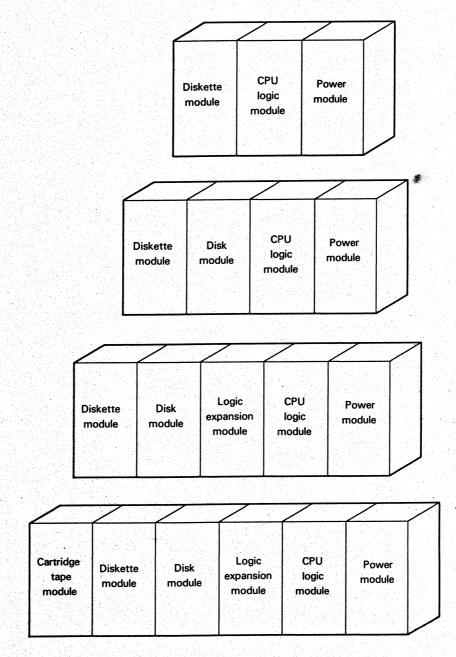

Figure 0-2 shows 3-, 4-, 5-, and 6-module configurations. Minimum configuration systems consist of a system console and a computer unit comprised of the three basic modules: power module, CPU logic module, and diskette module. Other modules can be added to expand upon the system's capabilities.

1. Power module, containing:

One power supply (if a 3-module system); or Two power supplies (if more than 3 modules in system) Cooling blower Line frequency clock generator card (optional)

2. CPU logic module, containing:

Two-board system processor unit featuring dual CPUs, basic system memory, and interface logic for system console, serial printer, and diskette subsystem 256 Kbyte or 512 Kbyte semiconductor memory cards (optional) with byte parity (for a maximum system memory capacity of 768 Kbytes) Color monitor interface board (optional)

One or more (as space permits) I/O interface cards (optional)

3. Diskette drive module, containing:

One or, optionally, two 5.25-inch diskette drives

4. Disk module, containing:

Disk controller card One 5.25-inch Winchester disk drive

5. Disk expansion unit, consisting of:

Disk module (less the controller)

Power module with one power supply and a cooling blower.

6. Cartridge tape module, containing:

Controller card 5.25-inch cartridge tape drive Power supply

7. 5-slot logic expansion module that accommodates up to five I/O interface cards

ID-00648

Figure 0-2 Models 10 or 10/SP system configuration

# **Organization**

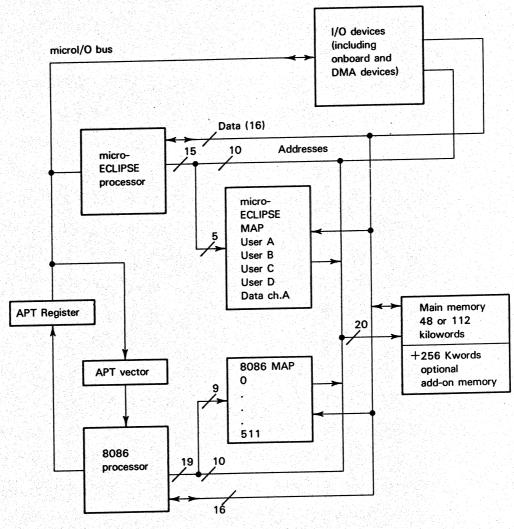

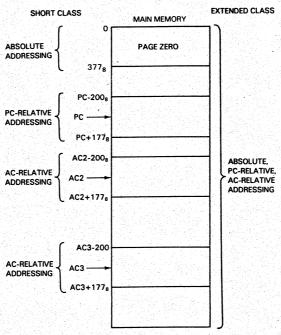

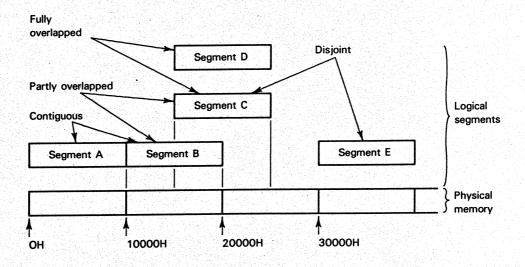

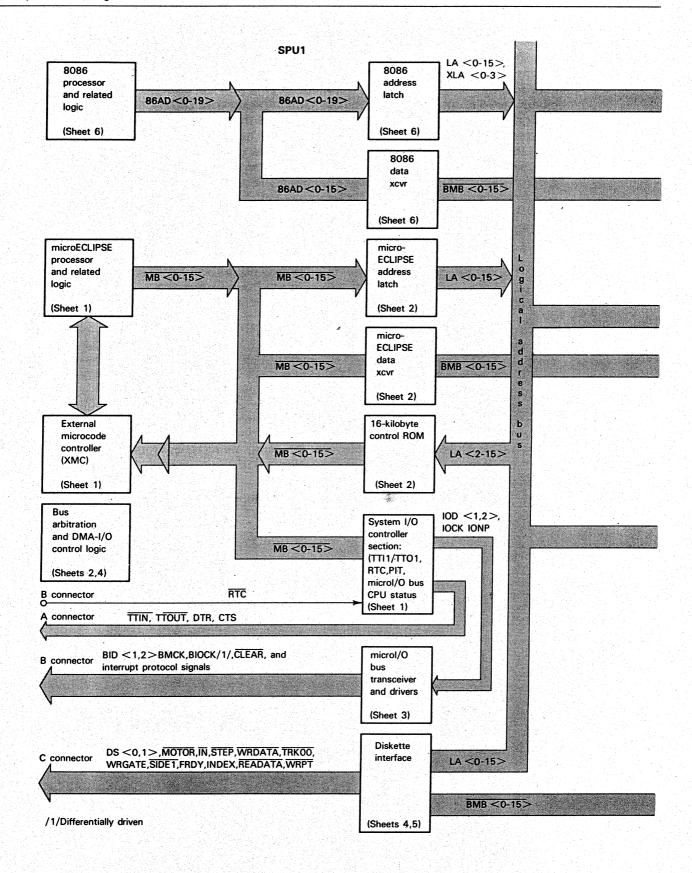

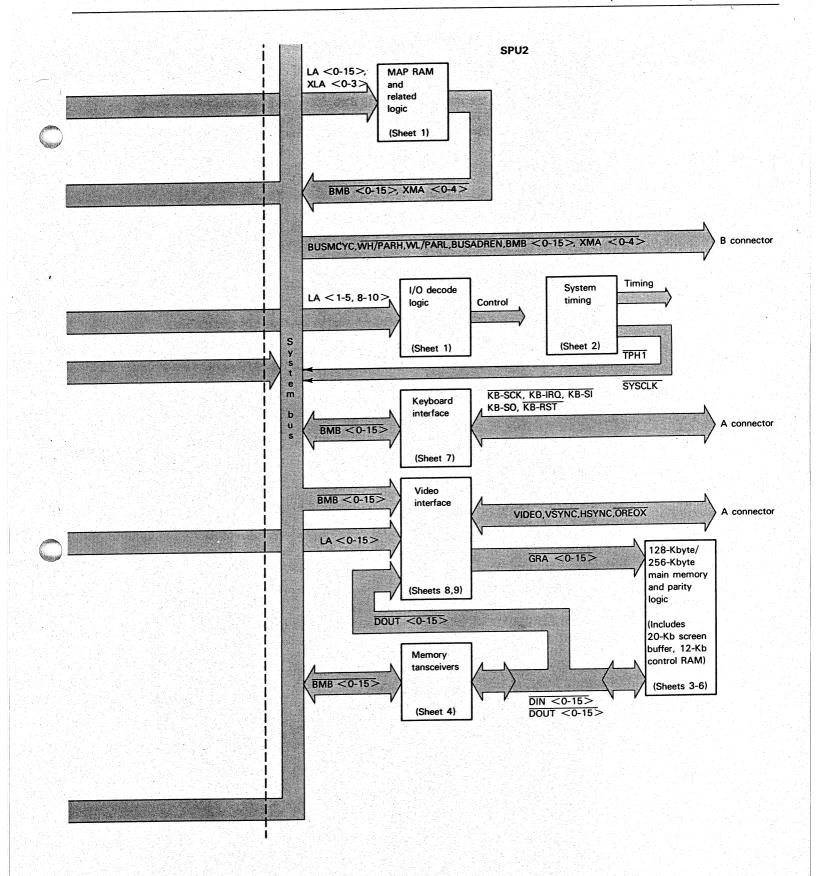

As shown in Figure 0-3, the two system processors (microECLIPSE and 8086) are organized around two major system buses: the memory bus and the microI/O bus. The memory bus provides a 16-bit wide, memory address/data path (address path expands to 20 bits wide in memory mapped mode) between the system processors and the memories, and the optional firmware floating point unit, when present. The microI/O bus (sometimes called the Microproducts or microNOVA I/O bus) consists of sixteen lines, four of which provide a differentially driven, 2-bit serial data path between the microECLIPSE processor and the I/O subsystems.

## Components

The components of the Model 10 and Model 10/SP systems are described below.

## System Processing Unit

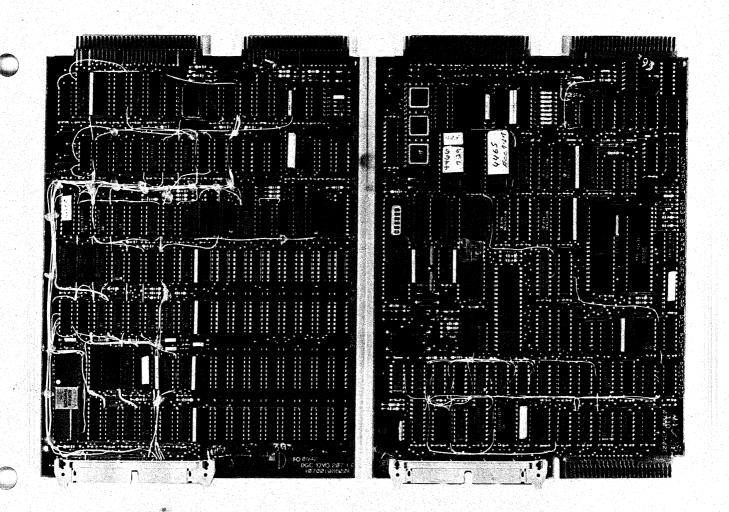

The two-board System Processing Unit (SPU) resides in slots 1 and 2 of the SPU logic module. These boards contain two CPUs: a microECLIPSE processor and an 8086 microprocessor.

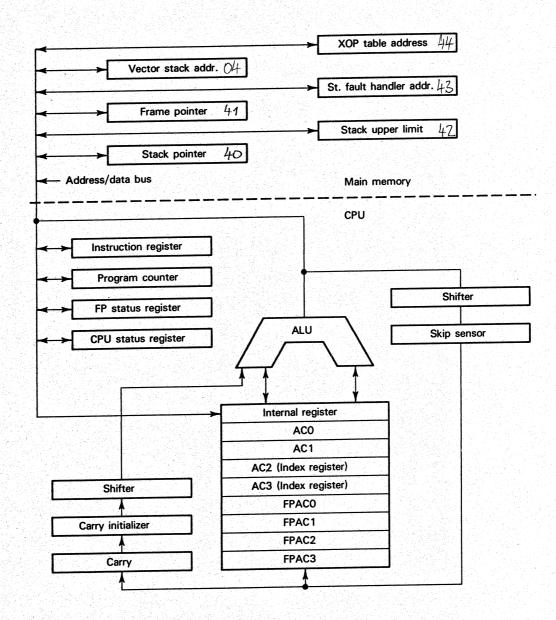

The microECLIPSE processor implements the 16-bit ECLIPSE character instruction set and supports Data General's RDOS, AOS, and MP/AOS-SU operating systems. It also supports bit-mapped graphics for the monochrome monitor and gives direct memory access (DMA) to graphics applications for rapid screen response. The microECLIPSE CPU can be supplied with or without a firmware floating point instruction set.

The 8086 microprocessor implements the Intel 8086 microprocessor instruction set, which supports the the MS-DOS and CP/M-86 operating systems.

The two SPU boards also contain:

- Basic system memory (128 kbytes or 256 kbytes)

- Memory allocation and protection unit (MAP)

- System console interface for the system console monitor and keyboard

- Diskette interface

- Serial printer interface (EIA RS-232-C compatible)

- Virtual console

- Real-time clock

- Programmable interval timer

- Parity checking logic for memory data

- Power status monitor

- Power-up diagnostics

- Program load logic

The two-board SPU provides basic, low-address RAM for system memory. It can be configured with either 128 Kbytes or 256 Kbytes of storage. The memory

arrays are structured with 64K by 1-bit elements of dynamic MOS random-access memory (RAM). The memory includes byte parity bits for data.

The parity checking logic of the SPU verifies the integrity of system memory. It appends a parity bit to each byte of data written to memory and checks it when it is read. When the parity checking logic is enabled by the program, a parity error generates a program interrupt.

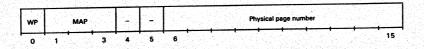

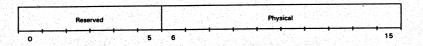

The MAP performs logical-to-physical address translation for the system memory. It also provides the following protection mechanisms: validity, write, I/O and indirection.

The system console interface port on the System Processing Unit communicates with the system console monitor and keyboard. For the optional 13-inch color monitor, a separate graphics controller board is used. Additional workstations for multiterminal operation are connected via the asynchronous communications interfaces (see the subsections "I/O Interfaces" and "Multiterminal workstations").

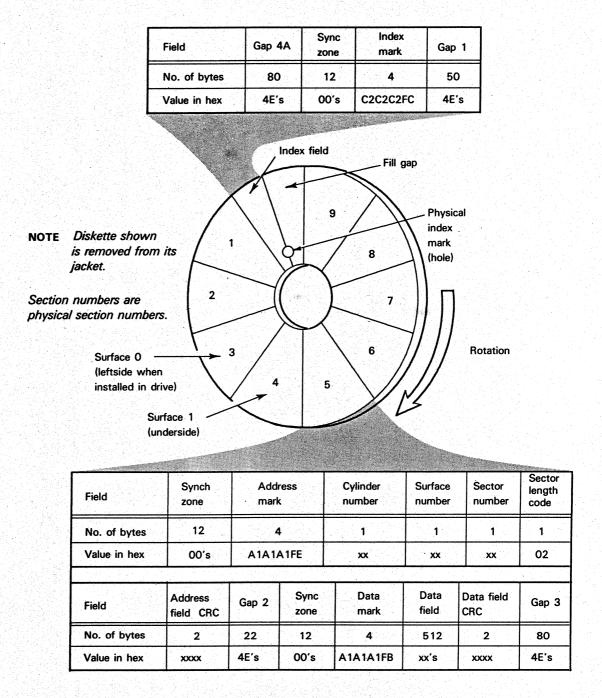

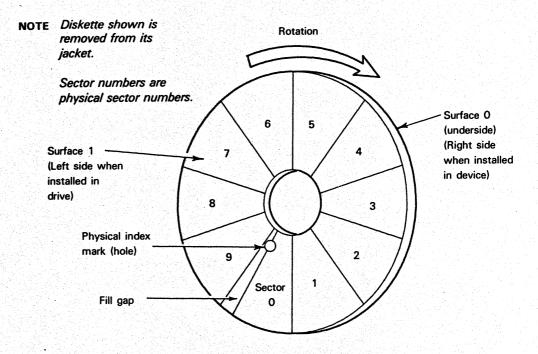

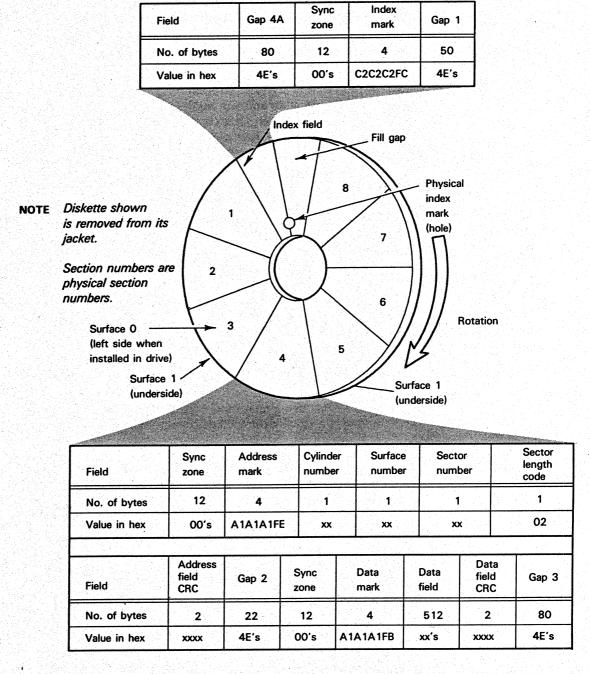

The diskette interface, which resides on the two-board SPU, can be programmed to read and write Data General formatted diskettes (9 sectors per track) or CPM and IBM PC formatted diskettes (8 sectors per track). The controller can also be programmed to read Data General's ENTERPRISE/MPT™ 5.25 inch, formatted diskettes (35 tracks per surface and 10 sectors per track).

The printer interface port on the SPU provides asynchronous communications with a connected serial printer. The interface conforms to EIA RS-232-C specifications.

The virtual console provides a firmware substitute for front panel switches and indicators, allowing the operator at the system console to program load; start, stop and continue program execution; and perform program debugging operations.

The real-time clock and programmable interval timer (PIT) provide time bases for programs that require them. The real-time clock generates low-frequency, I/O interrupts at one of the following program-selectable rates: 10 Hz, 100 Hz, 1,000 Hz, or ac line frequency. The PIT can be programmed to generate I/O interrupts at fixed intervals ranging from 100 microseconds to 6.5536 seconds. The clock rate of the PIT is 10 KHz.

The power status monitor tracks the state of a power status signal supplied by the power supply and initiates a power fail interrupt whenever power falls outside specified limits.

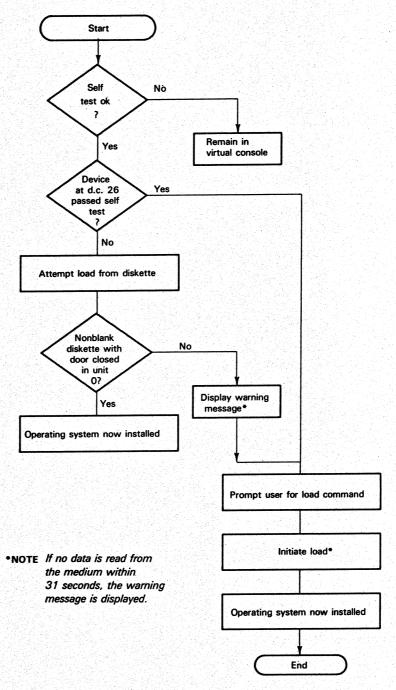

The power-up diagnostic — a thirty- to forty-five second self-test routine — verifies the basic integrity of the system each time power is applied. It checks all of memory, the virtual console, the CPU, the system console interface, the attached processor, the MAP units, the printer port, and the color video interface, if present.

The program-load logic — this feature automatically transfers a low-level bootstrap program from the diskette drive and is initiated after a successful completion of the power-up self-test diagnostics if no disk drive is present in the system. The low-level bootstrap program is then executed to initiate the transfer of subsequent program elements of the operating system.

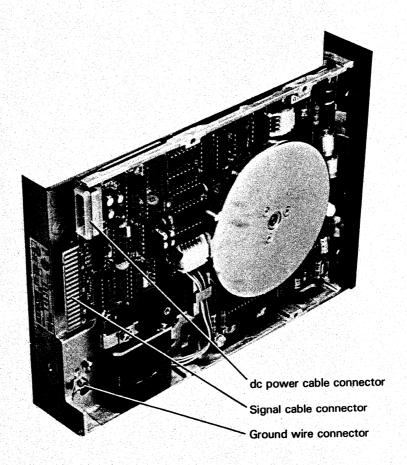

# Diskette Subsystem

The diskette module contains one or, optionally, two drives that reside in the diskette module. Each drive stores and retrieves data from a 5.25 inch, double-sided, low-track density (48 tracks per inch) diskette containing 40 tracks per surface. There can be 8 to 10 sectors per track, depending on the type of diskette.

Each sector stores 512 bytes of data. The diskette interface uses direct memory accessing to transfer 8-bit data bytes between memory and the subsystem.

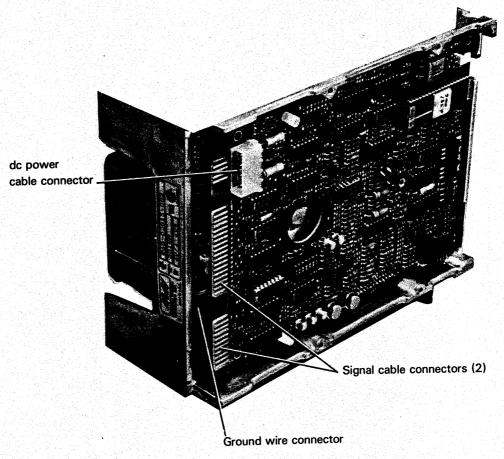

#### Disk Subsystem

The optional disk subsystem consists of a disk controller and up to two 5.25-inch, Winchester disk drives with a formatted storage capacity of 15 megabytes per drive.

The controller and one disk drive reside within the disk module of the main computer unit. The second disk drive, when present, resides in an expansion unit, consisting of a disk module and a power module with one power supply assembly. An external device cable connects the second disk drive to the subsystem controller.

Each drive stores and retrieves data from 5.25-inch, double-sided, fixed disk platters, containing 306 tracks per surface — 305 tracks for the user and one for diagnostics. Each track contains 17 sectors and each sector stores 512 bytes of data. The controller provides a sector buffer for data transfers and uses the microI/O bus and data channel facility of the SPU to transfer 16-bit data words between memory and the subsystem.

## Video Interface

An optional video interface board can be added for a 13-inch color graphics monitor. The video interface board will reside in the slot next to SPU2 in the CPU logic module.

# System Console

The system console consists of a 12-inch monochrome monitor and keyboard. It allows the user to direct the activities of the system. This console connects to interface logic on the SPU. If an optional color video interface board is included, a 13-inch color monitor can be substituted for the monochrome monitor in the system console.

## **Multiterminal Workstations**

Up to four additional terminals can be connected for multiterminal operation. These terminals connect directly to any of the optional asynchronous communications interfaces: Models 4463-Z, 4463-W. Any of the following DASHER™ model terminals may be used: D210, D211, G300, D410, and D460.

# Cartridge Tape Subsystem

The optional cartridge tape subsystem consists of a controller, a 1/4 inch magnetic tape cartridge drive, a fan, and a power supply. The subsystem provides a storage capacity of up to 15.4 Mbytes. The controller uses the microI/O bus and standard data channel facility of the CPU to transfer 16-bit data words between memory and the subsystem.

#### I/O Interfaces

The Model 10 and Model 10/SP support a selection of asynchronous/synchronous communications multiplexors and sensor I/O subsystems. Each card occupies an I/O slot in either the CPU logic module or the 5-slot expansion module and communicates with the CPU via the microI/O bus.

The asynchronous communications facilities provide an EIA-RS232C or 20 MA current-loop line interface, jumper-selectable, for the several DASHER $^{\text{m}}$  display terminals available as additional workstations.

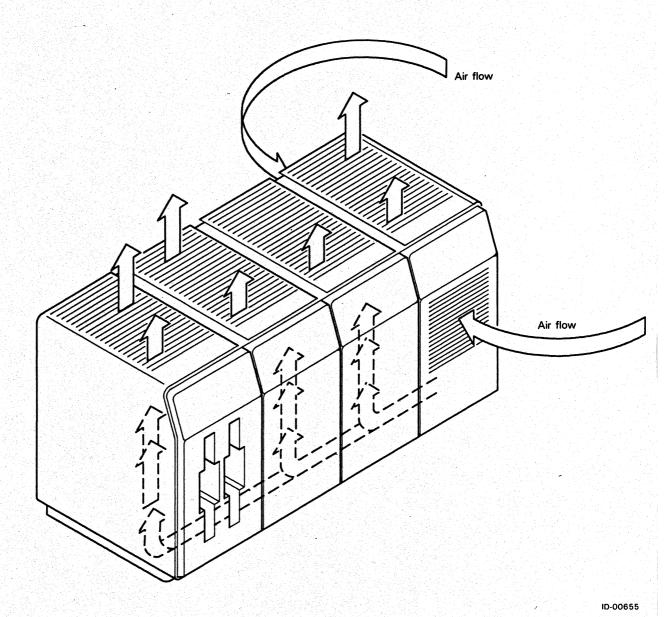

## Power Subsystem

The power subsystem consists of one or two, 123-watt (output), power supply assemblies and a cooling blower inside the power module. The power module also houses an optional line frequency clock generator card. One power supply assembly provides dc power to the CPU logic module and diskette subsystem while the second power assembly supports the disk module and optional 5-slot expansion module.

#### TECHNICAL SPECIFICATIONS

Table 0-1 through Table 0-5 list general specifications as well as mechanical, electrical, and environmental specifications for the Model 10 and Model 10/SP computer systems.

Table 0-1 General specifications

| Unit                  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Model 10<br>System    | Minimum 3-module system contains: CPU logic module which System includes dual-CPU system processing unit and 128 Kbytes of system memory, a diskette module with one 5.25-inch diskette drive, and a power module containing one power supply and a cooling blower.                                                                                                                                                                                                                                                                                            |

|                       | Additions to the minimum configuration can include up to 512 Kbytes of additional memory, a second diskette drive (housed in same module as the first drive), a disk module containing a 15-Mbyte Winchester disk subsystem (this also requires the addition of a second power supply unit in the power supply module), and a cartridge tape module with its own interna power supply. A second disk drive can also be configured and is housed in a separate two-module unit: a disk module and power supply module with one power supply and cooling blower. |

| Model 10/SP<br>System | This configuration supports AOS and MP/AOS-SU operating systems. Includes the same features as the Model 10 and has a firmware floating point option.                                                                                                                                                                                                                                                                                                                                                                                                          |

| System<br>Console     | Each system has one 12-inch monochrome display terminal with a keyboard that are used for system operator functions as well as user applications. A 13-inch color monitor is optional.                                                                                                                                                                                                                                                                                                                                                                         |

11

Table 0-2 General specifications, basic components

| Unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| System<br>Processing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Unit (SPU)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | System location                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | CPU logic module, slots 1 and 2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |